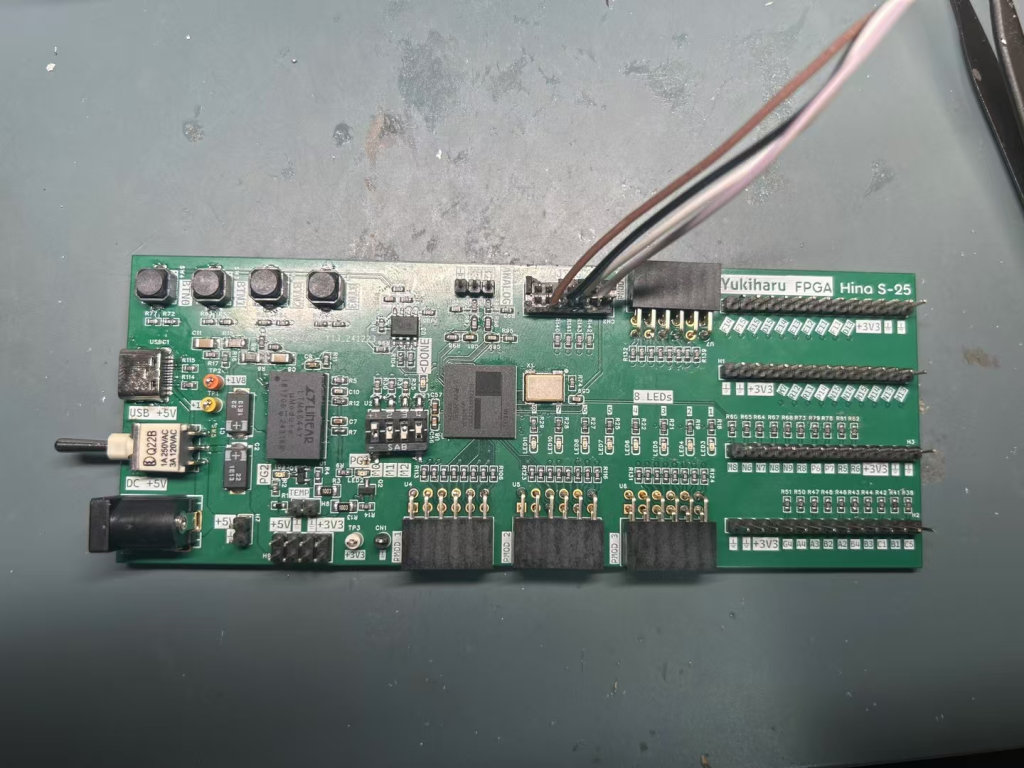

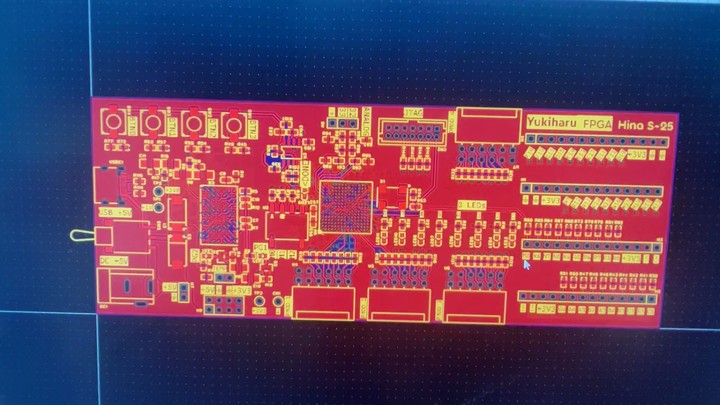

[2024年末收官] Yukiharu Hina S-25 自制FPGA开发板

自制开发板系列!

项目从12月初开始搞,中间打样工厂那边又遇到一些问题,但还是在2024年底完成了!

PCB一共花了6层,两层电源,四层信号

注意:此板子设计用于低速项目,的所有IO脚都没有做等长和阻抗匹配,请勿用于高速或差分数字信号的操作

简单介绍

- FPGA: Xlinx Spartan 7 XC7S25

- 32Mbit SPI FLASH (可用于下载固化程序)

- 50MHz 有源晶振

- 8个用户LED

- 4个用户按钮

- 4个PMOD连接器(32个数字IO,3.3V level)

- 40个数字IO(3.3V level)

- 2个模拟输入

- 可以选择从USB TypeC或者DC接口取电

- 给PMOD模块和取电针脚最大可以提供8A,峰值10A的3.3V电压

- JTAG连接器,用于调试和下载程序

- 电源模块温度传感器针脚(模拟,独立)

- DONE状态LED

- 2个电源模块POWER GOOD状态LED(3.3V)

- 每个IO都串接了200ohm的电阻,防止用户误操作短路导致烧坏FPGA

开发小记

做这个项目是为了给FPGA Audio Equalizer项目制作FPGA主控的breakout,兼做一个用来调试算法(例如滤波器,效果器等)的小板。选择Spartan 7是因为他功耗较低(因为我们的Equalizer想要做成500模块的类型,power budget比较有限),而且价格相对比较便宜。逻辑资源和DSP slice数量适中,适合我们的项目应用。

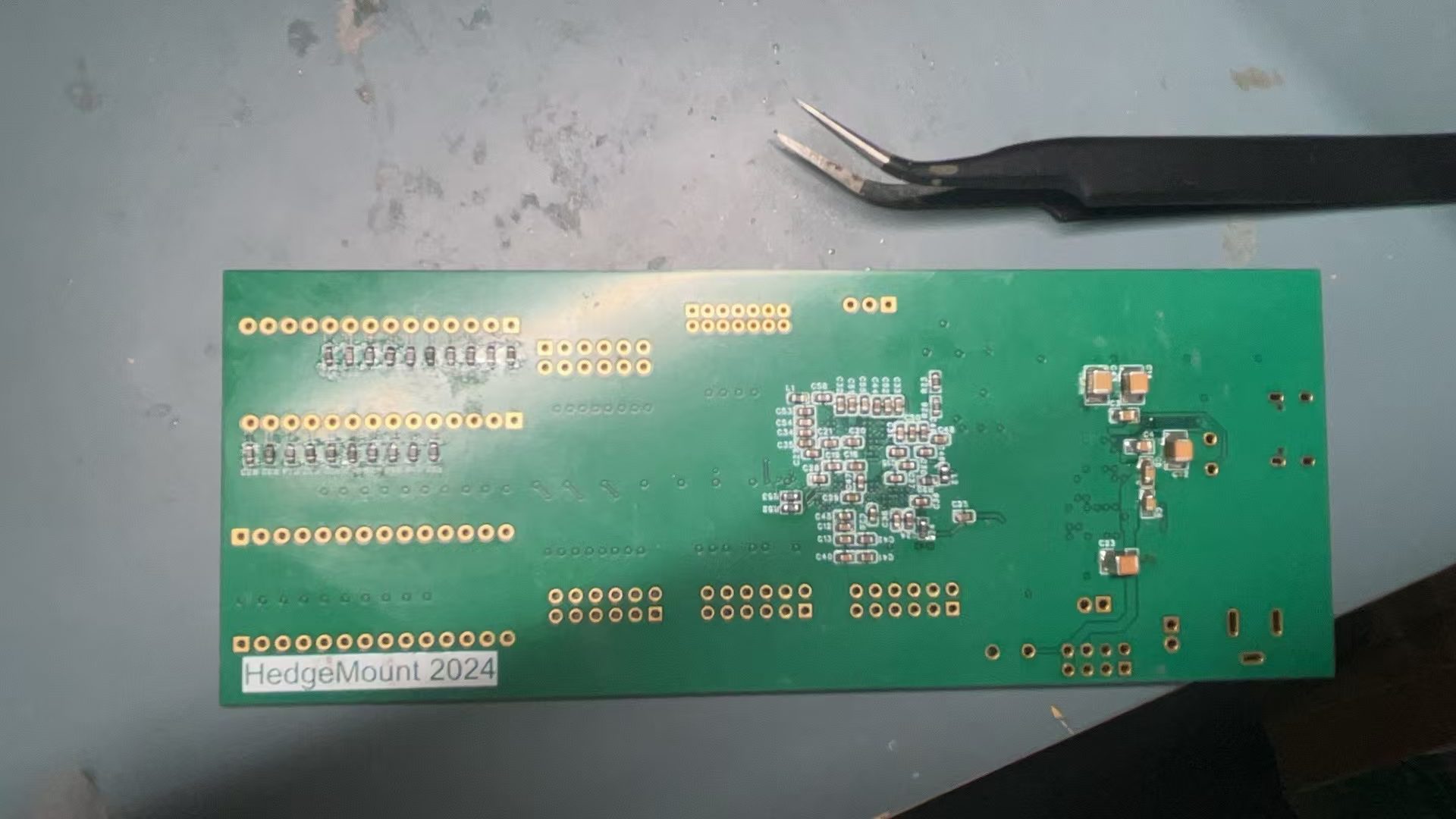

上图:背面展示

在本次设计schematic和layout的过程中也学到了很多有关的内容,例如:

- Xilinx要求上电时序,此FPGA需要按照这样的顺序: 1.0V -> 1.8V -> 3.3V

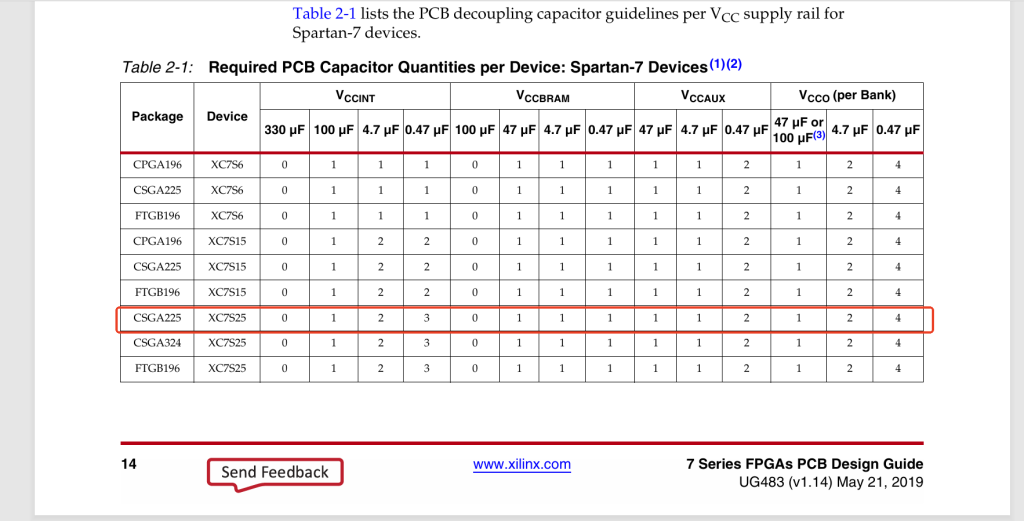

- 滤波电容和去耦电容的大小和数量在Xilinx的文档中有要求和推荐型号

- 尤其是FPGA部分,注意滤波电容和去耦电容的位置要尽可能靠近引脚

细说:

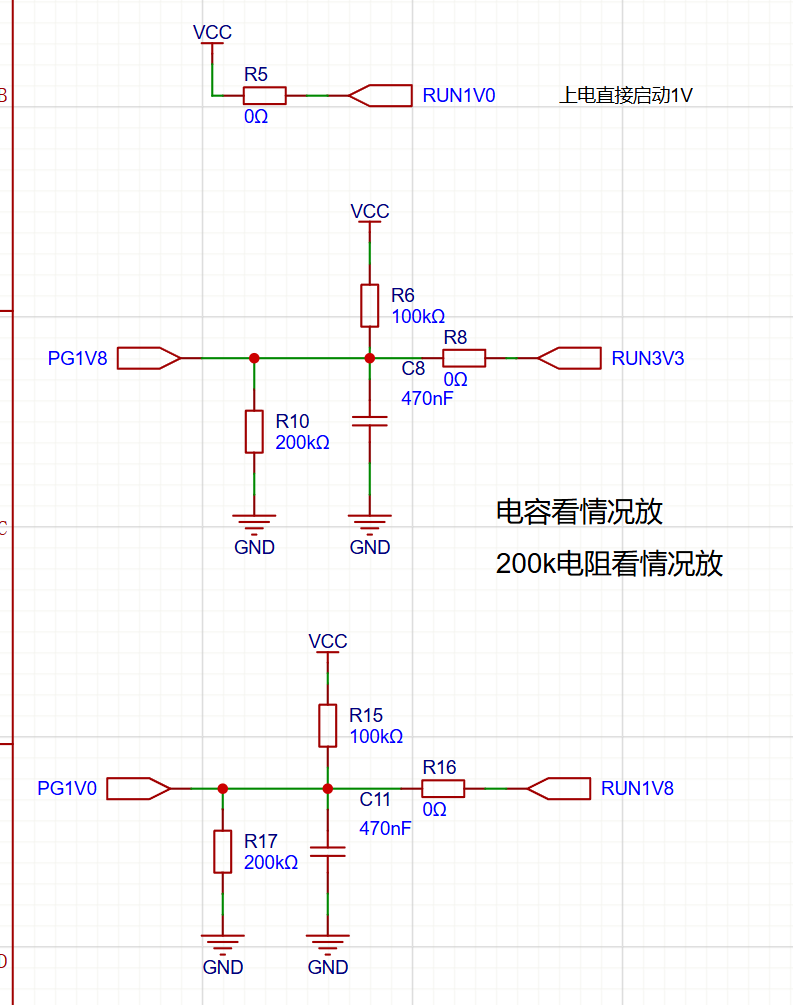

1. 电源与上电时序

这次画板的时候使用了ADI的LTM4644降压模块,这个模块有四路4A最大5A的独立输出,也可以把两路合并成一路进行输出。所以在我的板子上,我分配了一路1.0V,一路1.8V,两路3.3V合并为一路输出(电流翻倍)。每一路又有单独的PGOOD电源准备好和EN使能,所以我就设计了如下图的结构来实现当前一个供电准备好以后直接触发下一个供电启动从而实现上电时序。

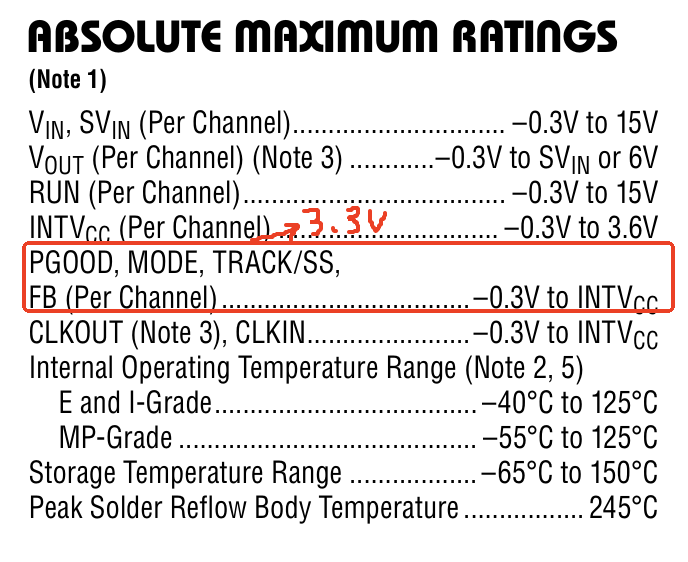

在设计的时候我标注了200k电阻看情况放(最终还是放了),这主要是因为在电源模块的datasheet中标明PGOOD承受电压最大值为INTVcc,同时PGOOD是一个open drain信号,在我的设计中INTVcc是3.3V,所以我不是很确定当VCC是5V的时候如果不加这个200k电阻来分压是否会导致PGOOD超压烧掉。RUN使能信号倒是无所谓,最大能到15V。等回学校以后我会向老师请教这个问题。同时也欢迎您在评论区分享您的见解。

数据表链接: https://www.analog.com/media/en/technical-documentation/data-sheets/LTM4644-4644-1.pdf

2. 滤波电容,去耦电容选型,数量和位置

这些信息都在Xilinx官方的文件中有说明。7系列每个型号的FPGA每个引脚的要求都列出来了,并且还有一些推荐的电容型号。

文件:UG483

链接: https://docs.amd.com/v/u/en-US/ug483_7Series_PCB

上图:红框圈起来的是我们使用的XC7S25的官方推荐

本次设计为了防止翻车,我也尽量选择了官方数据表中推荐的电容型号(基本是村田,太诱这些牌子,价格有点高,可以找一下平替型号)

测试程序

我只做了一个简单的按键和流水灯测试程序来测试板子上的功能都好用,并把他下载固化到了板载flash上从而测定flash以及config拨码开关是否好用。

top.v:

`timescale 1ns / 1ps

module top(

leds [7:0],

clk,

btns [3:0]

);

input clk;

input [3:0] btns;

output reg [7:0] leds = 'b0;

parameter MCNT=24999999;

reg [24:0]counter;

always@(posedge clk)begin

if(counter==MCNT)

counter <=0;

else

counter <= counter+1'b1;

end

always@(posedge clk) begin

if(btns[0] == 'b1) begin

leds <= 'b0000_0001;

end else begin

if(btns[1] == 'b1) begin

leds <= 'b0000_0010;

end else begin

if(btns[2] == 'b1) begin

leds <= 'b0000_0100;

end else begin

if(btns[3] == 'b1) begin

leds <= 'b0000_1000;

end else begin

if(counter==MCNT)

if(leds == 'b1111_1111) begin

leds <= 'b0;

end else begin

leds <= (leds << 1) + 'b1;

end

else

leds <= leds;

end

end

end

end

end

endmodule

constraint约束文件:

set_property PACKAGE_PIN E2 [get_ports led]

set_property SLEW SLOW [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN M9 [get_ports clk]

set_property PACKAGE_PIN F2 [get_ports {leds[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[0]}]

set_property PACKAGE_PIN D3 [get_ports {leds[6]}]

set_property PACKAGE_PIN E3 [get_ports {leds[5]}]

set_property PACKAGE_PIN C4 [get_ports {leds[4]}]

set_property PACKAGE_PIN E1 [get_ports {leds[3]}]

set_property PACKAGE_PIN J1 [get_ports {leds[2]}]

set_property PACKAGE_PIN K1 [get_ports {leds[1]}]

set_property PACKAGE_PIN E2 [get_ports {leds[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {btns[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {btns[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {btns[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {btns[0]}]

set_property PACKAGE_PIN D4 [get_ports {btns[3]}]

set_property PACKAGE_PIN B5 [get_ports {btns[2]}]

set_property PACKAGE_PIN D1 [get_ports {btns[1]}]

set_property PACKAGE_PIN D2 [get_ports {btns[0]}]

Demo测试视频

demo测试的时候为了调试方便没焊所有的直插件

总结和一些遗憾

总的来说还是比较成功的。6层板打样的时候工厂拖了几天才生产好发货,差点就没能焊完。我没有BGA焊台,贴不上FPGA芯片(225pin BGA),需要找人贴。最后是在走之前跑去信息城找修笔记本的朋友帮我焊的。

下一步的硬件project就是画ZYNQ的核心板,同样也是为我们的调音台项目做准备。正在考虑是否自己画一个JTAG下载器debugger。

一些遗憾:

- 没仔细读datasheet,选择电源输入的开关画板的时候方向画反了,本来设计的是向哪个方向拨动就选择哪个电源,但是现在方向是反的。例如,拨向Type-C则会从DC插头取电,反之亦然

- JTAG插座买错了。应该选2.54mm(100mil)针间距,但是错选成了1mm针间距,导致我的调试器没法直接插上,最后因为赶时间所以用水口钳把塑料部分掰碎了,然后直接飞了四条线来下载的程序

原理图和PCB

时间仓促,还没整理好,等我整理好以后会发出来

Discussion

New Comments

No comments yet. Be the first one!